AP 3302 Pt. 3

Section 2

CHAPTER 5

Clamping Circuits

D

to E. Since the diode is cut off, C can only discharge very slowly on a long

time constant of CR seconds and Vc falls slightly from +75V. Both VR

and Vout rise by the same amount as Vc falls.

D

to E. Since the diode is cut off, C can only discharge very slowly on a long

time constant of CR seconds and Vc falls slightly from +75V. Both VR

and Vout rise by the same amount as Vc falls.

E to F. The input rises by 100V from zero. VR therefore rises by the same amount and so does Vout, Vc remaining constant. VR rises to a slightly positive value and the diode cuts on.

F to G. With the diode conducting, C recharges on a short time constant of CRD seconds and Vc rises quickly to + 75V. VR returns to zero in the same time (producing the usual pip) and Vout returns to the bias level of + 25V.

Thereafter the cycle is repeated and the output is negatively clamped to the positive bias level of + 25V. Examination of Fig. 7b will show that the output waveform is merely that of VR superimposed on the bias level.

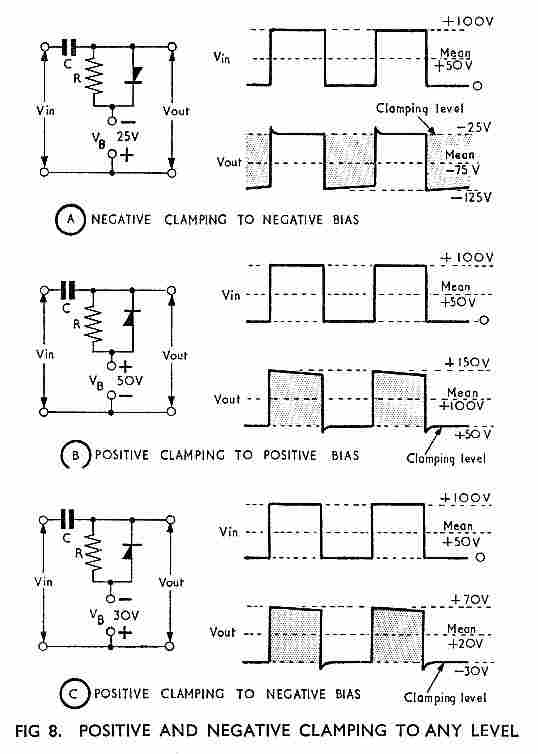

If the bias polarity is reversed then the output waveform is negatively clamped to a negative bias level of 25V (Fig. 8a). Positive clamping to a bias voltage is achieved simply by reversing the connections to the diode. Fig. 8b shows positive clamping to a positive bias level of 50V and Fig. 8c shows positive clamping to a negative bias level of 30V.

In practice, positive or negative clamping to almost any voltage level is required. We shall see examples of this later in these notes.