AP 3302 Pt. 3

Section 2

CHAPTER 11

Frequency-Dividing & Counting Circuits

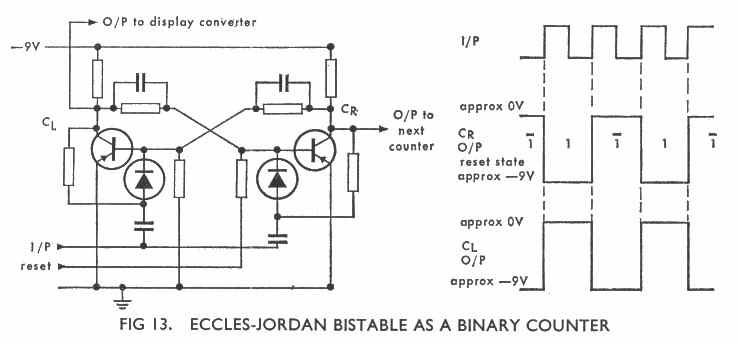

Bistable as a binary counter.

The basic circuit action of an Eccles-Jordan bistable was discussed on p 127. Inclusion of two diodes in the base input leads (Fig 13) means that the circuit will only change states on a positive going edge of the trigger input, ie once per cycle. Thus for two cycles of input the bistable will change states twice, producing one cycle of output. This means that the circuit is dividing or counting by two and it is therefore called a binary counter. Such bistable circuits may be used in combination in a register to provide counts in powers of two. With two bistables connected in cascade, one output cycle indicates a count of 22 = 4; for three circuits in cascade an output is obtained for every 23 = 8 input cycles and so on.

Before the count begins all bistables are reset by

momentarily open-circuiting the reset line (normally earthed). This causes a

negative voltage at the base of the right-hand transistor which therefore conducts

and its collector will then be at approximately zero volts. A positive edge

is produced at the output every time the bistable changes over from 1 to  ("not

1") and this is used to trigger the next bistable in a cascade counter.

("not

1") and this is used to trigger the next bistable in a cascade counter.

By introducing suitable feedback, a four stage cascaded counter can be made to count by ten instead of sixteen. This is a very common arrangement in computers and in test equipment such as frequency counters.